Most Updated Digital Circuits MCQs – New Counters MCQs ( Digital Circuits ) MCQs

Latest Digital Circuits MCQs

By practicing these MCQs of Counters MCQs ( Digital Circuits ) MCQs – Latest Competitive MCQs , an individual for exams performs better than before. This post comprising of objective questions and answers related to “ Counters MCQs ( Digital Circuits ) Mcqs “. As wise people believe “Perfect Practice make a Man Perfect”. It is therefore practice these mcqs of Digital Circuits to approach the success. Tab this page to check ” Counters MCQs ( Digital Circuits )” for the preparation of competitive mcqs, FPSC mcqs, PPSC mcqs, SPSC mcqs, KPPSC mcqs, AJKPSC mcqs, BPSC mcqs, NTS mcqs, PTS mcqs, OTS mcqs, Atomic Energy mcqs, Pak Army mcqs, Pak Navy mcqs, CTS mcqs, ETEA mcqs and others.

Digital Circuits MCQs – Counters MCQs ( Digital Circuits ) MCQs

The most occurred mcqs of Counters MCQs ( Digital Circuits ) in past papers. Past papers of Counters MCQs ( Digital Circuits ) Mcqs. Past papers of Counters MCQs ( Digital Circuits ) Mcqs . Mcqs are the necessary part of any competitive / job related exams. The Mcqs having specific numbers in any written test. It is therefore everyone have to learn / remember the related Counters MCQs ( Digital Circuits ) Mcqs. The Important series of Counters MCQs ( Digital Circuits ) Mcqs are given below:

Counters

1. In digital logic, a counter is a device which ____________

a) Counts the number of outputs

b) Stores the number of times a particular event or process has occurred

c) Stores the number of times a clock pulse rises and falls

d) Counts the number of inputs

Answer: b

Explanation: In digital logic and computing, a counter is a device which stores (and sometimes displays) the number of times a particular event or process has occurred, often in relationship to a clock signal.

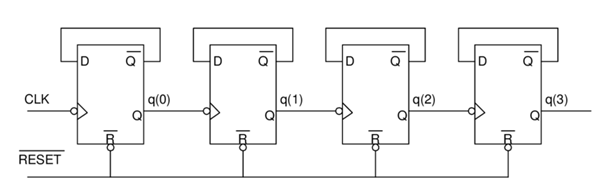

2. A counter circuit is usually constructed of ____________

a) A number of latches connected in cascade form

b) A number of NAND gates connected in cascade form

c) A number of flip-flops connected in cascade

d) A number of NOR gates connected in cascade form

Answer: c

Explanation: A counter circuit is usually constructed of a number of flip-flops connected in cascade. Preferably, JK Flip-flops are used to construct counters and registers.

3. What is the maximum possible range of bit-count specifically in n-bit binary counter consisting of ‘n’ number of flip-flops?

a) 0 to 2n

b) 0 to 2n + 1

c) 0 to 2n – 1

d) 0 to 2n+1/2

Answer: c

Explanation: The maximum possible range of bit-count specifically in n-bit binary counter consisting of ‘n’ number of flip-flops is 0 to 2n-1. For say, there is a 2-bit counter, then it will count till 22-1 = 3. Thus, it will count from 0 to 3.

4. How many types of the counter are there?

a) 2

b) 3

c) 4

d) 5

Answer: b

Explanation: Counters are of 3 types, namely, (i)asynchronous/synchronous, (ii)single and multi-mode & (iii)modulus counter. These further can be subdivided into Ring Counter, Johnson Counter, Cascade Counter, Up/Down Counter and such like.

5. A decimal counter has ______ states.

a) 5

b) 10

c) 15

d) 20

Answer: b

Explanation: Decimal counter is also known as 10 stage counter. So, it has 10 states. It is also known as Decade Counter counting from 0 to 9.

6. Ripple counters are also called ____________

a) SSI counters

b) Asynchronous counters

c) Synchronous counters

d) VLSI counters

Answer: b

Explanation: Ripple counters are also called asynchronous counter. In Asynchronous counters, only the first flip-flop is connected to an external clock while the rest of the flip-flops have their preceding flip-flop output as clock to them.

7. Synchronous counter is a type of ____________

a) SSI counters

b) LSI counters

c) MSI counters

d) VLSI counters

Answer: c

Explanation: Synchronous Counter is a Medium Scale Integrated (MSI). In Synchronous Counters, the clock pulse is supplied to all the flip-flops simultaneously.

8. Three decade counter would have ____________

a) 2 BCD counters

b) 3 BCD counters

c) 4 BCD counters

d) 5 BCD counters

Answer: b

Explanation: Three decade counter has 30 states and a BCD counter has 10 states. So, it would require 3 BCD counters. Thus, a three decade counter will count from 0 to 29.

9. BCD counter is also known as ____________

a) Parallel counter

b) Decade counter

c) Synchronous counter

d) VLSI counter

Answer: b

Explanation: BCD counter is also known as decade counter because both have the same number of stages and both count from 0 to 9.

10. The parallel outputs of a counter circuit represent the _____________

a) Parallel data word

b) Clock frequency

c) Counter modulus

d) Clock count

Answer: d

Explanation: The parallel outputs of a counter circuit represent the clock count. A counter counts the number of times an event takes place in accordance to the clock pulse.

Asynchronous Counter

1. How many natural states will there be in a 4-bit ripple counter?

a) 4

b) 8

c) 16

d) 32

Answer: c

Explanation: In an n-bit counter, the total number of states = 2n.

Therefore, in a 4-bit counter, the total number of states = 24 = 16 states.

2. A ripple counter’s speed is limited by the propagation delay of _____________

a) Each flip-flop

b) All flip-flops and gates

c) The flip-flops only with gates

d) Only circuit gates

Answer: a

Explanation: A ripple counter is something that is derived by other flip-flops. It’s like a series of Flip Flops. Output of one FF becomes the input of the next. Because ripple counter is composed of FF only and no gates are there other than FF, so only propagation delay of FF will be taken into account. Propagation delay refers to the amount of time taken in producing an output when the input is altered.

3. One of the major drawbacks to the use of asynchronous counters is that ____________

a) Low-frequency applications are limited because of internal propagation delays

b) High-frequency applications are limited because of internal propagation delays

c) Asynchronous counters do not have major drawbacks and are suitable for use in high- and low-frequency counting applications

d) Asynchronous counters do not have propagation delays, which limits their use in high-frequency applications

Answer: b

Explanation: One of the major drawbacks to the use of asynchronous counters is that High-frequency applications are limited because of internal propagation delays. Propagation delay refers to the amount of time taken in producing an output when the input is altered.

4. Internal propagation delay of asynchronous counter is removed by ____________

a) Ripple counter

b) Ring counter

c) Modulus counter

d) Synchronous counter

Answer: d

Explanation: Propagation delay refers to the amount of time taken in producing an output when the input is altered. Internal propagation delay of asynchronous counter is removed by synchronous counter because clock input is given to each flip-flop individually in synchronous counter.

5. What happens to the parallel output word in an asynchronous binary down counter whenever a clock pulse occurs?

a) The output increases by 1

b) The output decreases by 1

c) The output word increases by 2

d) The output word decreases by 2

Answer: b

Explanation: In an asynchronous counter, there isn’t any clock input. The output of 1st flip-flop is given to second flip-flop as clock input. So, in case of binary down counter the output word decreases by 1.

6. How many flip-flops are required to construct a decade counter?

a) 4

b) 8

c) 5

d) 10

Answer: a

Explanation: Number of flip-flop required is calculated by this formula: 2(n-1) <= N< = 2n. 24=16and23=8, therefore, 4 flip flops needed.

7. The terminal count of a typical modulus-10 binary counter is ____________

a) 0000

b) 1010

c) 1001

d) 1111

Answer: c

Explanation: A binary counter counts or produces the equivalent binary number depending on the cycles of the clock input. Modulus-10 means count from 0 to 9. So, the terminal count is 9 (1001).

8. How many different states does a 3-bit asynchronous counter have?

a) 2

b) 4

c) 8

d) 16

Answer: c

Explanation: In a n-bit counter, the total number of states = 2n.

Therefore, in a 3-bit counter, the total number of states = 23 = 8 states.

9. A 5-bit asynchronous binary counter is made up of five flip-flops, each with a 12 ns propagation delay. The total propagation delay (tp(total)) is ____________

a) 12 ms

b) 24 ns

c) 48 ns

d) 60 ns

Answer: d

Explanation: Since a counter is constructed using flip-flops, therefore, the propagation delay in the counter occurs only due to the flip-flops. Each bit has propagation delay = 12ns. So, 5 bits = 12ns * 5 = 60ns.

10. An asynchronous 4-bit binary down counter changes from count 2 to count 3. How many transitional states are required?

a) 1

b) 2

c) 8

d) 15

Answer: d

Explanation: Transitional state is given by (2n – 1). Since, it’s a 4-bit counter, therefore, transition states = 24 – 1 = 15. So, total transitional states are 15.

11. A 4-bit ripple counter consists of flip-flops, which each have a propagation delay from clock to Q output of 15 ns. For the counter to recycle from 1111 to 0000, it takes a total of ____________

a) 15 ns

b) 30 ns

c) 45 ns

d) 60 ns

Answer: d

Explanation: Since a counter is constructed using flip-flops, therefore, the propagation delay in the counter occurs only due to the flip-flops. One bit change is 15 ns, so 4-bit change = 15 * 4 = 60.

12. Three cascaded decade counters will divide the input frequency by ____________

a) 10

b) 20

c) 100

d) 1000

Answer: d

Explanation: Decade counter has 10 states. So, three decade counters are cascaded i.e. 10*10*10=1000 states.

13. A ripple counter’s speed is limited by the propagation delay of ____________

a) Each flip-flop

b) All flip-flops and gates

c) The flip-flops only with gates

d) Only circuit gates

Answer: a

Explanation: A ripple counter is something that is derived by other flip-flops. Its like a series of Flip Flops. Output of one FF becomes the input of the next. Because ripple counter is composed of FF only and no gates are there other than FF, so only propagation delay of FF will be taken into account. Propagation delay refers to the amount of time taken in producing an output when the input is altered.

14. A 4-bit counter has a maximum modulus of ____________

a) 3

b) 6

c) 8

d) 16

Answer: d

Explanation: In a n-bit counter, the total number of states = 2n.

Therefore, in a 4-bit counter, the total number of states = 24 = 16 states.

15. A principle regarding most display decoders is that when the correct input is present, the related output will switch ____________

a) HIGH

b) To high impedance

c) To an open

d) LOW

Answer: d

Explanation: A principle regarding most display decoders is that when the correct input is present, the related output will switch LOW. Since it’s an active-low device.

Counter ICs

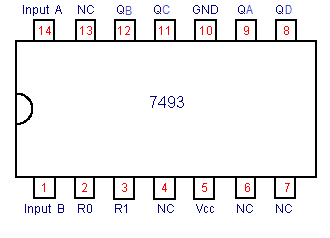

1. What is the difference between a 7490 and a 7493?

a) 7490 is a MOD-10, 7493 is a MOD-16

b) 7490 is a MOD-16, 7493 is a MOD-10

c) 7490 is a MOD-12, 7493 is a MOD-16

d) 7490 is a MOD-10, 7493 is a MOD-12

Answer: a

Explanation: The difference between a 7490 and a 7493 is that 7490 is a MOD-10, 7493 is a MOD-16 counter. Thus, 7490 traverses 10 states and 7493 traverses 16 states.

2. How many different states does a 2-bit asynchronous counter have?

a) 1

b) 4

c) 2

d) 8

Answer: b

Explanation: For a n-bit counter, total number of states = 2n. Thus, for 2-bit counter, total number of states = 22 = 4.

3. A 12 MHz clock frequency is applied to a cascaded counter containing a modulus-5 counter, a modulus-8 counter, and a modulus-10 counter. The lowest output frequency possible is ________

a) 10 kHz

b) 20 kHz

c) 30 kHz

d) 60 kHz

Answer: c

Explanation: Cascaded counter containing a modulus-5 counter, a modulus-8 counter, and a modulus-10 counter. So, 5*8*10=400. Applied clock frequency = 12 MHz; hence, the lowest output frequency possible is 12MHz/400=30 kHz.

4. Which one is a 4-bit binary ripple counter?

a) IC 7493

b) IC 7490

c) IC 7491

d) IC 7492

Answer: b

Explanation: IC 7493 is a 4-bit binary ripple counter. It is a MOD-16 counter with 24 = 16 states.

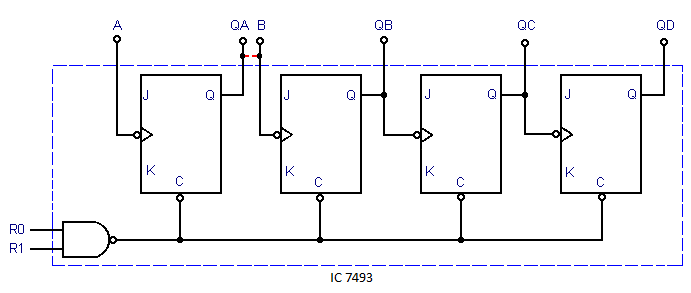

5. IC 7493 consist of ____________

a) 4 S-R flip-flop

b) 4 J-K flip-flop

c) 4 master-slave flip-flop

d) 4 D flip-flop

Answer: c

Explanation: IC 7493 consist of 4 J-K master-slave flip-flop. It is a MOD-16 counter with 24 = 16 states.

6. A reset input is used in IC 7493, why?

a) For increment of bit by 1

b) For decrement of bit by 1

c) For reset the counter

d) For setting the counter

Answer: c

Explanation: The reset inputs are used to reset the counter to 0000.

7. In a 4-bit binary ripple counter, four master-slave flip-flops are internally connected to provide a ________ bit counter.

a) Divide-by-2 & divide-by-6

b) Divide-by-6 & divide-by-8

c) Divide-by-2 & divide-by-8

d) Divide-by-4 & divide-by-8

Answer: c

Explanation: In a 4-bit binary ripple counter, four master-slave flip-flops are internally connected to provide a Divide-by-2 & divide-by-8 bit counter.

8. Which of the following is a decade counter?

a) IC 7493

b) IC 7490

c) IC 7491

d) IC 7492

Answer: b

Explanation: IC 7490 is called as decade counter or MOD-10. Thus, it has 10 states.

9. In a 4-bit decade counter, four master-slave flip-flops are internally connected to provide a ________ bit counter.

a) Divide-by-2 & divide-by-6

b) Divide-by-6 & divide-by-8

c) Divide-by-2 & divide-by-5

d) Divide-by-4 & divide-by-8

Answer: c

Explanation: In a decade counter, four master-slave flip-flops are internally connected to provide a Divide-by-2 & divide-by-5 bit counter.

10. Reset inputs are used in IC 7490, why?

a) For increment of bit by 1

b) For decrement of bit by 1

c) For reset the counter

d) For setting the counter

Answer: c

Explanation: The reset inputs are used to reset the counter to 0000.

11. The set inputs are used in a decade counter, why?

a) To set the counter to 0011

b) To set the counter to 1000

c) To set the counter to 1001

d) To set the counter to 0001

Answer: c

Explanation: The set inputs are used in a decade counter to set the counter to 1001 which is 9 in decimal, as a decade counter counts from 0 to 9.

12. List which pins need to be connected together on a 7493 to make a MOD-12 counter.

a) 12 to 1, 11 to 3, 9 to 2

b) 12 to 1, 11 to 3, 12 to 2

c) 12 to 1, 11 to 3, 8 to 2

d) 12 to 1, 11 to 3, 1 to 2

Answer: c

Explanation: IC-7493 is a MOD-16 counter. So maximum, it can have 16 states. A MOD-12 counter will have 12-states. Thus, it is clear from the diagram shown below: 12 & 1 are clear pins, 11 & 3 are clock pins, 8 & 2 are input for 7493 FF.

13. Ripple counter IC has _____________

a) 10 pins

b) 11 pins

c) 12 pins

d) 14 pins

Answer: d

Explanation: A ripple counter is of 4-bit and has 4 J-K flip-flops. Ripple counter IC has 14 pins.

14. Integrated-circuit counter chips are used in numerous applications including ____________

a) Timing operations, counting operations, sequencing, and frequency multiplication

b) Timing operations, counting operations, sequencing, and frequency division

c) Timing operations, decoding operations, sequencing, and frequency multiplication

d) Data generation, counting operations, sequencing, and frequency multiplication

Answer: b

Explanation: There are no integrated circuit counter chips employed for frequency multiplication. In the rest of the options, frequency multiplication is mentioned which is not related to counters in anyway. So, they are not the correct answers. Thus, counters are used for timing operations, counting operations, sequencing and frequency division.

15. What is the difference between 7490 and a 7492?

a) 7490 is a MOD-12, 7492 is a MOD-10

b) 7490 is a MOD-12, 7492 is a MOD-16

c) 7490 is a MOD-16, 7492 is a MOD-10

d) 7490 is a MOD-10, 7492 is a MOD-12

Answer: d

Explanation: From the properties of both ICs, we have 7490 is a MOD-10, 7492 is a MOD-12. Thus, IC-7490 can have maximum 10 states, while IC-7492 can have maximum 12 states.

Asynchronous Down Counter

1. Which of the following statements are true?

a) Asynchronous events does not occur at the same time

b) Asynchronous events are controlled by a clock

c) Synchronous events does not need a clock to control them

d) Only asynchronous events need a control clock

Answer: a

Explanation: Asynchronous events does not occur at the same time because of propagation delay and they do need a clock pulse to trigger them. Whereas, synchronous events occur in presence of clock pulse.

2. A down counter using n-flip-flops count ______________

a) Downward from a maximum count

b) Upward from a minimum count

c) Downward from a minimum to maximum count

d) Toggles between Up and Down count

Answer: a

Explanation: As the name suggests down counter means counting occurs from a higher value to lower value (i.e. (2^n – 1) to 0).

3. UP Counter is ____________

a) It counts in upward manner

b) It count in down ward manner

c) It counts in both the direction

d) Toggles between Up and Down count

Answer: a

Explanation: UP counter counts in an upward manner from 0 to (2n – 1).

4. DOWN counter is ____________

a) It counts in upward manner

b) It count in downward manner

c) It counts in both the direction

d) Toggles between Up and Down count

Answer: b

Explanation: DOWN counter counts in a downward manner from (2n – 1) to 0.

5. How many different states does a 3-bit asynchronous down counter have?

a) 2

b) 4

c) 6

d) 8

Answer: d

Explanation: In a n-bit counter, the total number of states = 2n.

Therefore, in a 3-bit counter, the total number of states = 23 = 8 states.

6. In a down counter, which flip-flop doesn’t toggle when the inverted output of the preceeding flip-flop goes from HIGH to LOW.

a) MSB flip-flop

b) LSB flip-flop

c) Master slave flip-flop

d) Latch

Answer: b

Explanation: Since the LSB flip-flop changes its state at each negative transition of clock. That is why LSB flip-flop doesn’t have toggle.

7. In a 3-bit asynchronous down counter, the initial content is ____________

a) 000

b) 111

c) 010

d) 101

Answer: a

Explanation: Initially, all the flip-flops are RESET. So, the initial content is 000. At the first negative transition of the clock, the counter content becomes 101.

8. In a 3-bit asynchronous down counter, at the first negative transition of the clock, the counter content becomes ____________

a) 000

b) 111

c) 101

d) 010

Answer: b

Explanation: Since, in the down counter, the counter content is decremented by 1 for every negative transition. Hence, in a 3-bit asynchronous down counter, at the first negative transition of the clock, the counter content becomes 111.

9. In a 3-bit asynchronous down counter, at the first negative transition of the clock, the counter content becomes ____________

a) 000

b) 111

c) 101

d) 010

Answer: c

Explanation: Since, in the down counter, the counter content is decremented by 1 for every negative transition. Hence, in a 3-bit asynchronous down counter, at the first negative transition of the clock, the counter content becomes 101.

10. The hexadecimal equivalent of 15,536 is ________

a) 3CB0

b) 3C66

c) 63C0

d) 6300

Answer: a

Explanation: You just divide the number by 16 at the end and store the remainder from bottom to top.

11. In order to check the CLR function of a counter ____________

a) Apply the active level to the CLR input and check all of the Q outputs to see if they are all in their reset state

b) Ground the CLR input and check to be sure that all of the Q outputs are LOW

c) Connect the CLR input to Vcc and check to see if all of the Q outputs are HIGH

d) Connect the CLR to its correct active level while clocking the counter; check to make sure that all of the Q outputs are toggling

Answer: a

Explanation: CLR stands for clearing or resetting all states of flip-flop. In order to check the CLR function of a counter, apply the active level to the CLR input and check all of the Q outputs to see if they are all in their reset state.

Propagation Delay in Ripple Counter

1. Modulus refers to ____________

a) A method used to fabricate decade counter units

b) The modulus of elasticity, or the ability of a circuit to be stretched from one mode to another

c) An input on a counter that is used to set the counter state, such as UP/DOWN

d) The maximum number of states in a counter sequence

Answer: d

Explanation: Modulus is defined as the maximum number of stages/states a counter has. It is independent of the number of states the counter will actually traverse.

2. A sequential circuit design is used to ____________

a) Count up

b) Count down

c) Decode an end count

d) Count in a random order

Answer: d

Explanation: A sequential circuit design is used to count in a random manner which is faster than the combinational circuit. It is used for storing data.

3. In general, when using a scope to troubleshoot digital systems, the instrument should be triggered by ____________

a) The A channel or channel 1

b) The vertical input mode, when using more than one channel

c) The system clock

d) Line sync, in order to observe troublesome power line glitches

Answer: c

Explanation: All the information is sent from one end to another end through the clock pulse which behaves like a carrier. So, for troubleshooting it should be triggered by the same. Since the system clock is internally produced.

4. Which counters are often used whenever pulses are to be counted and the results displayed in decimal?

a) Synchronous

b) Bean

c) Decade

d) BCD

Answer: d

Explanation: BCD means Binary Coded Decimal, which means that decimal numbers coded of binary numbers. It displays the decimal equivalent of corresponding binary numbers.

5. The ________ counter in the Altera library has controls that allow it to count up or down, and perform synchronous parallel load and asynchronous cascading.

a) 74134

b) LPM

c) Synchronous

d) AHDL

Answer: b

Explanation: The library of parameterized modules (LPM) counter in the Altera library has controls that allow it to count up or down, and perform synchronous parallel load and asynchronous cascading.

6. The minimum number of flip-flops that can be used to construct a modulus-5 counter is ____________

a) 3

b) 8

c) 5

d) 10

Answer: a

Explanation: The minimum number of flip-flops used in a counter is given by: 2(n-1)<=N<=2n.

Thus, for modulus-5 counter: 22 <= N <= 23, where N = 5 and n = 3.

7. The duty cycle of the most significant bit from a 4-bit (0–9) BCD counter is ____________

a) 20%

b) 50%

c) 10%

d) 80%

Answer: a

Explanation: There are 10 states, out of which MSB is high only for (1000, 1001) 2 times. Hence duty cycle is 2/10*100 = 20%. Since the duty cycle is the ratio of on-time to the total time.

8. Normally, the synchronous counter is designed using ____________

a) S-R flip-flops

b) J-K flip-flops

c) D flip-flops

d) T flip-flops

Answer: b

Explanation: Since J-K flip-flops have options of recovery from toggle condition and by using less number of J-K flip-flops a synchronous counter can be designed. So, it is more preferred. Also, because JK-flip-flops resolves the problem of Forbidden States.

9. MOD-16 counter requires ________ no. of states.

a) 8

b) 4

c) 16

d) 32

Answer: c

Explanation: 2n >= N >= 2(n-1), by using this formula we get the value of N=16 for n=4.

10. What is a state diagram?

a) It provides the graphical representation of states

b) It provides exactly the same information as the state table

c) It is same as the truth table

d) It is similar to the characteristic equation

Answer: b

Explanation: The state diagram provides exactly the same information as the state table and is obtained directly from the state table.

11. High speed counter is ____________

a) Ring counter

b) Ripple counter

c) Synchronous counter

d) Asynchronous counter

Answer: c

Explanation: Synchronous counter doesn’t have propagation delay. Propagation delay refers to the amount of time taken in producing the output when the input is altered.

12. Program counter in a digital computer ____________

a) Counts the number of programs run in the machine

b) Counts the number of times a subroutine

c) Counts the number of time the loops are executed

d) Points the memory address of the current or the next instruction

Answer: d

Explanation: Program counter in a digital computer points the memory address of the current or the next instruction which is to be executed.

13. Fundamental mode is another name for ____________

a) Level operation

b) Pulse operation

c) Clock operation

d) Edge operation

Answer: b

Explanation: Whatever the input given to the devices are in the form of pulses always. That is why it is known as a fundamental mode.

Counter Implementation and Applications

1. A ripple counter’s speed is limited by the propagation delay of ____________

a) Each flip-flop

b) All flip-flops and gates

c) The flip-flops only with gates

d) Only circuit gates

Answer: a

Explanation: A ripple counter is something that is derived by other flip-flops. It’s like a series of Flip Flops. The output of one FF becomes the input of the next. Because ripple counter is composed of FF only and no gates are there other than FF, so only propagation delay of FF will be taken into account. Propagation delay refers to the amount of time taken in producing an output when the input is altered.

2. A 5-bit asynchronous binary counter is made up of five flip-flops, each with a 12 ns propagation delay. The total propagation delay (tp(tot)) is ________

a) 12 ms

b) 24 ns

c) 48 ns

d) 60 ns

Answer: d

Explanation: Since a counter is constructed using flip-flops, therefore, the propagation delay in the counter occurs only due to the flip-flops. Each bit has propagation delay = 12ns. So, 5 bits = 12ns * 5 = 60ns.

3. A 4-bit ripple counter consists of flip-flops, which each have a propagation delay from clock to Q output of 15 ns. For the counter to recycle from 1111 to 0000, it takes a total of ________

a) 15 ns

b) 30 ns

c) 45 ns

d) 60 ns

Answer: d

Explanation: Since a counter is constructed using flip-flops, therefore, the propagation delay in the counter occurs only due to the flip-flops. Each bit has propagation delay = 15ns. So, 4 bits = 15ns * 4 = 60ns.

4. A ripple counter’s speed is limited by the propagation delay of __________

a) Each flip-flop

b) All flip-flops and gates

c) The flip-flops only with gates

d) Only circuit gates

Answer: a

Explanation: A ripple counter is something that is derived by other flip-flops. Its like a series of Flip Flops. Output of one FF becomes the input of the next. Because ripple counter is composed of FF only and no gates are there other than FF, so only propagation delay of FF will be taken into account. Propagation delay refers to the amount of time taken in producing an output when the input is altered.

5. What is the maximum delay that can occur if four flip-flops are connected as a ripple counter and each flip-flop has propagation delays of tPHL = 22 ns and tPLH = 15 ns?

a) 15 ns

b) 22 ns

c) 60 ns

d) 88 ns

Answer: d

Explanation: Maximum propagation delay is the longest delay between an input changing value and the output changing value. Hence, 22 * n = 22*4 (Since there are 4 FFs) = 88ns.

6. The main drawback of a ripple counter is that __________

a) It has a cumulative settling time

b) It has a distributive settling time

c) It has a productive settling time

d) It has an associative settling time

Answer: a

Explanation: The main drawback of a ripple counter is that it has a cumulative settling time (i.e. another bit is transmitted just after one consequently).

7. A 4 bit modulo-16 ripple counter uses JK flip-flops. If the propagation delay of each flip-flop is 50 nsec, the maximum clock frequency that can be used is equal to __________

a) 20 MHz

b) 10 MHz

c) 5 MHz

d) 4 MHz

Answer: c

Explanation: Since a counter is constructed using flip-flops, therefore, the propagation delay in the counter occurs only due to the flip-flops. Each bit has propagation delay = 50ns. So, 4 bits or FFs = 50ns * 4 = 200ns. Clock frequency = 1/200ns = 5 MHz.

8. As the number of flip flops are increased, the total propagation delay of __________

a) Ripple counter increases but that of synchronous counter remains the same

b) Both ripple and synchronous counters increase

c) Both ripple and synchronous counters remain the same

d) Ripple counter remains the same but that of synchronous counter increases

Answer: a

Explanation: In ripple counter, the clock pulses are applied to one flip-flop only. Hence, as the number of flip-flops increases the delay increases. In the synchronous counter, clock pulses to all flip-flops are applied simultaneously.

9. A reliable method for eliminating decoder spikes is the technique called ________

a) Strobing

b) Feeding

c) Wagging

d) Waving

Answer: a

Explanation: A reliable method for eliminating decoder spikes is the technique called strobing. A strobe signal validates the availability of data on consecutive parallel lines.

10. A glitch that appears on the decoded output of a ripple counter is often difficult to see on an oscilloscope because of __________

a) It is a random event

b) It occurs less frequently than the normal decoded output

c) It is very fast

d) All of the Mentioned

Answer: d

Explanation: A glitch is a transition that occurs before a signal settles to a specific value. A glitch that appears on the decoded output of a ripple counter is often difficult to see on an oscilloscope because it is a random event and very fast and it occurs less frequently than the normal decoded output.

11. Assume a 4-bit ripple counter has a failure in the second flip-flop such that it “locks up”. The third and fourth stages will __________

a) Continue to count with correct outputs

b) Continue to count but have incorrect outputs

c) Stop counting

d) Turn into molten silicon

Answer: c

Explanation: The ripple counter would stop counting because next flip-flop’s input depends on the output of the previous flip-flop.

Up Down Counter

1. UP-DOWN counter is a combination of ____________

a) Latches

b) Flip-flops

c) UP counter

d) Up counter & down counter

Answer: d

Explanation: As the name suggests UP-DOWN, it means that it has up-counter and down-counter as well. It alternatively counts up and down.

2. UP-DOWN counter is also known as ___________

a) Dual counter

b) Multi counter

c) Multimode counter

d) Two Counter

Answer: c

Explanation: UP-DOWN counter is also known as multimode counter because it has capability of counting upward as well as downwards.

3. In an UP-counter, each flip-flop is triggered by ___________

a) The output of the next flip-flop

b) The normal output of the preceding flip-flop

c) The clock pulse of the previous flip-flop

d) The inverted output of the preceding flip-flop

Answer: b

Explanation: In an UP-counter, each flip-flop is triggered by the normal output of the preceding flip-flop. UP-counter counts from 0 to a maximum value.

4. In DOWN-counter, each flip-flop is triggered by ___________

a) The output of the next flip-flop

b) The normal output of the preceding flip-flop

c) The clock pulse of the previous flip-flop

d) The inverted output of the preceding flip-flop

Answer: d

Explanation: In DOWN-counter, each flip-flop is triggered by the inverted output of the preceding flip-flop. DOWN-counter counts from a maximum value to 0.

5. Binary counter that count incrementally and decrement is called ___________

a) Up-down counter

b) LSI counters

c) Down counter

d) Up counter

Answer: a

Explanation: Binary counter that counts incrementally and decrement is called UP-DOWN counter/multimode counter. It alternately counts up and down.

6. Once an up-/down-counter begins its count sequence, it ___________

a) Starts counting

b) Can be reversed

c) Can’t be reversed

d) Can be altered

Answer: d

Explanation: In up/down ripple counter once the counting begins, we can simply change the pulse M (mode control) M = 0 or 1 respectively for UP counter or Down counter.

7. In 4-bit up-down counter, how many flip-flops are required?

a) 2

b) 3

c) 4

d) 5

Answer: c

Explanation: An n-bit bit counter requires n number of FFs. In a 4-bit up-down counter, there are 4 J-K flip-flops required.

8. A modulus-10 counter must have ________

a) 10 flip-flops

b) 4 Flip-flops

c) 2 flip-flops

d) Synchronous clocking

Answer: b

Explanation: 2n-1 < = N < = 2n

For modulus-10 counter, N = 10. Therefore, 23 < = 10 < = 24. Thus, n = 4, and therefore, we require 4 FFs.

9. Which is not an example of a truncated modulus?

a) 8

b) 9

c) 11

d) 15

Answer: a

Explanation: An n-bit counter whose modulus is less than the maximum possible is called a truncated counter. Here, 9, 11 and 15 modulus counters are truncated counters. Whereas, modulus-8 is not a truncated counter.

10. The designation means that the ________

a) Up count is active-HIGH, the down count is active-LOW

b) Up count is active-LOW, the down count is active-HIGH

c) Up and down counts are both active-LOW

d) Up and down counts are both active-HIGH

Answer: a

Explanation: The designation means that the up count is active-HIGH, the down count is active-LOW. Active-High means that up-count would be triggered when clock is 1 else when clock is 0, down-count would be triggered, which is referred to as Active-low.

11. An asynchronous binary up counter, made from a series of leading edge-triggered flip-flops, can be changed to a down counter by ________

a) Taking the output on the other side of the flip-flops (instead of Q)

b) Clocking of each succeeding flip-flop from the other side (instead of Q)

c) Changing the flip-flops to trailing edge triggering

d) All of the Mentioned

Answer: d

Explanation: By all of the mentioned ideas, an asynchronous binary up counter, made from a series of leading edge-triggered flip-flops, can be changed to a down counter. Edge-triggered FFs refer to FFs being triggered during a clock transition from LOW to HIGH or HIGH to LOW.

12. A 4-bit binary up counter has an input clock frequency of 20 kHz. The frequency of the most significant bit is ________

a) 1.25 kHz

b) 2.50 kHz

c) 160 kHz

d) 320 kHz

Answer: a

Explanation: Input clock is given by 20/2 kHz. So, count on the basis of 10 kHz clock. And MSB changes on 8th stage; Hence, f = 10/8 = 1.25 kHz.